SG.hu·

Újabb nagy ugrásra készül a Rambus

A Rambus teljesen új memória architektúrát fejleszt, amely az órajel megsokszorozásával eleinte másodpercenként 16 gigabites, hosszabb távon pedig akár 1 terabyte-os sávszélességet is elérhet.

A Terabyte Bandwidth Initiative névre keresztelt projekt célja egy olyan architektúra kidolgozása, amely a következő évtized elejétől eddig soha nem látott sávszélességet biztosítana a memóriák terén. Ezt az órajel folyamatos növelése helyett annak felszorzásával, a sávszélesség drasztikus megugrásával érnék el, a technológia pedig nyitott lenne a további skálázásra, illetve finomításokra, amely újabb nagy lépéseket eredményezne - belátható időn belül.

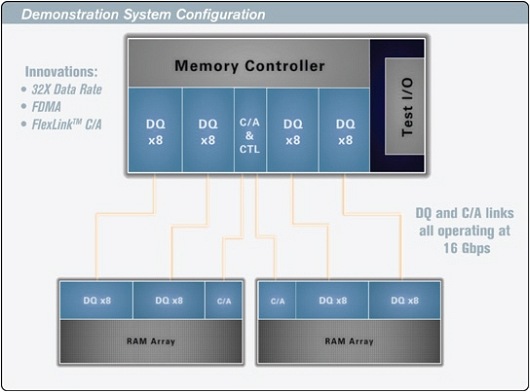

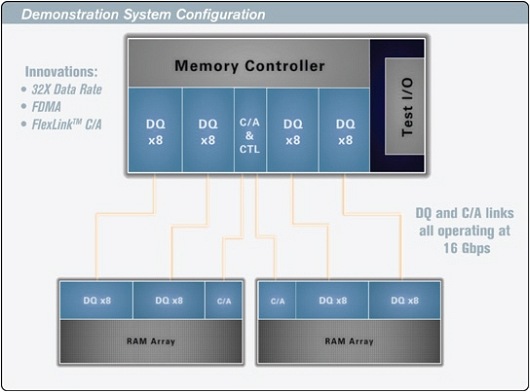

A nagy különbség a jelenleg elérhető DDR memóriák és a Rambus új fejlesztése között, hogy míg előbbi megkettőzi az órajelet, utóbbi egészen pontosan 32-szeresére növeli azt, sokkal nagyobb sávszélességet eredményezve ezzel. Konkrét példában ez annyit tesz, hogy míg egy 500 MHz-es DDR3 1 gigabitet ereszt át másodpercenként, az új tesztpéldányok akár 16 Gbps-ot is elérhetnek ugyanazon az órajelen és mindez csak az első lépést jelenti. A végső a másodpercenkénti 1 terabyte elérése, ezt pedig system on a chip (SoC) architektúrával, akár 16 DRAM egyidejű alkalmazásával érnék el.

Természetesen a sávszélesség növelését, illetve annak további skálázását számos egyéb változtatás és új fejlesztés teszi majd lehetővé, a pontos technikai részletekről a cég weboldalán tájékozódhatunk. Ezzel nemcsak a jelenleg elérhető DDR memóriákat, de a szintén a Rambus által fejlesztett 4,8 GHz-es XDR DRAM-ot is maguk mögött hagyják majd. A cég a következő generációs sokmagos alkalmazásokhoz, játékokhoz és grafikus fejlesztésekhez ajánlja a platformot.

Bár már elkészültek az első prototípussal, ebben azonban emulált DRAM chipeken tesztelik a sebességet, amelyek a Rambus saját vezérlőjére csatlakoznak, legfeljebb 64 Gbps-os sávszélen. A megoldást ezen a héten mutatják be Tokióban, a Rambus Developer Forum alatt. A kereskedelmi forgalomban megjelenő végleges változatra azonban még várni kell, hiszen erre a cég szerint legkorábban csak 2011-ben kerülhet sor.

A Terabyte Bandwidth Initiative névre keresztelt projekt célja egy olyan architektúra kidolgozása, amely a következő évtized elejétől eddig soha nem látott sávszélességet biztosítana a memóriák terén. Ezt az órajel folyamatos növelése helyett annak felszorzásával, a sávszélesség drasztikus megugrásával érnék el, a technológia pedig nyitott lenne a további skálázásra, illetve finomításokra, amely újabb nagy lépéseket eredményezne - belátható időn belül.

A nagy különbség a jelenleg elérhető DDR memóriák és a Rambus új fejlesztése között, hogy míg előbbi megkettőzi az órajelet, utóbbi egészen pontosan 32-szeresére növeli azt, sokkal nagyobb sávszélességet eredményezve ezzel. Konkrét példában ez annyit tesz, hogy míg egy 500 MHz-es DDR3 1 gigabitet ereszt át másodpercenként, az új tesztpéldányok akár 16 Gbps-ot is elérhetnek ugyanazon az órajelen és mindez csak az első lépést jelenti. A végső a másodpercenkénti 1 terabyte elérése, ezt pedig system on a chip (SoC) architektúrával, akár 16 DRAM egyidejű alkalmazásával érnék el.

Természetesen a sávszélesség növelését, illetve annak további skálázását számos egyéb változtatás és új fejlesztés teszi majd lehetővé, a pontos technikai részletekről a cég weboldalán tájékozódhatunk. Ezzel nemcsak a jelenleg elérhető DDR memóriákat, de a szintén a Rambus által fejlesztett 4,8 GHz-es XDR DRAM-ot is maguk mögött hagyják majd. A cég a következő generációs sokmagos alkalmazásokhoz, játékokhoz és grafikus fejlesztésekhez ajánlja a platformot.

Bár már elkészültek az első prototípussal, ebben azonban emulált DRAM chipeken tesztelik a sebességet, amelyek a Rambus saját vezérlőjére csatlakoznak, legfeljebb 64 Gbps-os sávszélen. A megoldást ezen a héten mutatják be Tokióban, a Rambus Developer Forum alatt. A kereskedelmi forgalomban megjelenő végleges változatra azonban még várni kell, hiszen erre a cég szerint legkorábban csak 2011-ben kerülhet sor.