SG.hu

2026-ban jönnek a TSMC első 1,6 nm-es chipjei

A tajvani székhelyű bérgyártó titán a Santa Clarában megrendezett North America Technology Symposium 2024 elnevezésű konferencián mutatta be a félvezető-feldolgozás, a tokozás és a 3D-s chiptechnológia terén elért legújabb fejlesztéseit.

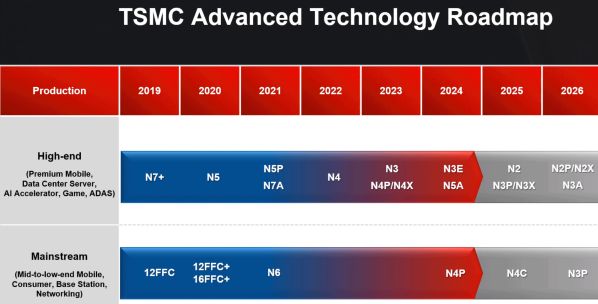

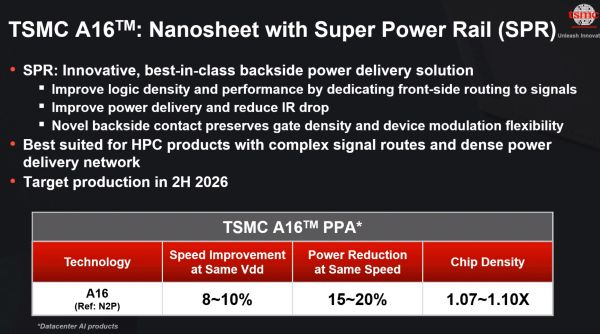

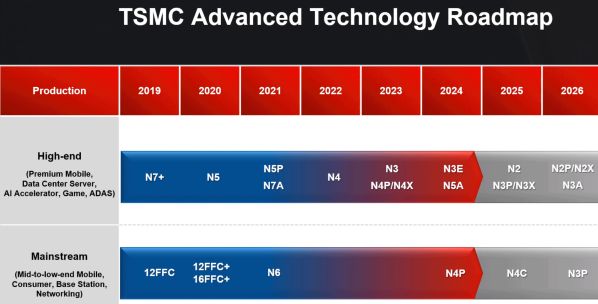

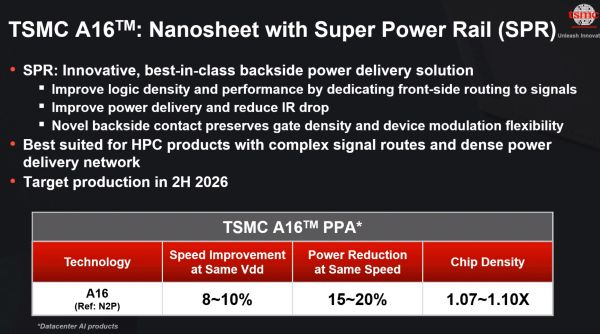

Az esemény főszereplője az A16 volt, mely a cég útitervének következő félvezető-feldolgozási technológiája. A betűszóban az A betű az angström rövidítése, egy nanométerben 10 angström van, így az A16 egy 1,6 nm-es eljárás - de a TSMC nem így hivatkozik rá. A TSMC ezt 2026-ban tervezi gyártásba venni, és az ebből készült szilícium 8-10 százalékos sebességnövekedést biztosít majd az N2P eljáráshoz képest, amely maga is a vállalat jövőre gyártásba kerülő 2 nm-es technológiájának továbbfejlesztett változata. A TSMC jelezte, hogy nincs szüksége az ASML legújabb High NA EUV fotolitográfiai gépeire az A16-os eljárásra való áttéréshez. Az iparágban egyesek azt sugallták, hogy az Intel le fogja előzni a TSMC-t, mert ők az első chipgyártó, amelyik ilyen géppel fog dolgozni.

A TSMC nyilvánosságra hozta, hogy az A16 a 2 nm-en bevezetésre kerülő tranzisztor dizájnt a Super Power Rail technológiával kombinálja majd. Ez utóbbi a vállalat "backside power" kialakítása, ahol a tranzisztorokhoz áramot szállító sávokat a szilícium hátoldalára helyezik át, hogy több jelsávnak adjanak helyet. Az Intel tavaly mutatta be az ilyen megoldását. Ez jobb logikai sűrűséget és teljesítményt kínál azáltal, hogy az elülső oldali útválasztást a jeleknek szenteli, így az A16 ideális az összetett jelútvonalakkal és sűrű tápellátó hálózatokkal rendelkező HPC-termékekhez - közölte a TSMC.

Az N2, azaz 2 nanométeres eljáráshoz a TSMC bejelentette a NanoFlexnek nevezett tervezési optimalizálási technikát. Ez rugalmasságot biztosít a chiptervezőknek a szabványos cellák építőblokkjaiban, lehetővé téve számukra, hogy a nagyobb energiahatékonyságot biztosító kisebb, és a maximális teljesítményt biztosító nagyobb cellák kombinációját úgy hangolják, hogy a legjobb teljesítmény- és területkompromisszumot érjék el az alkalmazásukhoz. A félvezetőóriás a 4 nm-es gyártástechnológiáját is frissítette, itt az újdonság neve N4C. Ez olyan területhatékony tervezési szabályokat tartalmaz, amelyek kompatibilisek a népszerű N4P eljárással, de a TSMC állítása szerint 8,5 százalékos gyártási költség-csökkenést eredményeznek. A sorozatgyártás beindítását 2025-re tervezik.

Csomagolástechnológia terén a TSMC bejelentette, hogy már gyártják az első System-on-Wafer (SoW) ajánlatukat, ami lehetővé teszi, hogy egy 300 mm-es ostyán nagyszámú lapka egyetlen rendszert alkosson. Ez növeli a számítási teljesítményt, miközben sokkal kevesebb helyet foglal. A vállalat közölte, hogy a tervek szerint 2027-re elkészül a Chip-on-Wafer változat, amely a Chip-on-Wafer-on-Substrate (CoWoS) technológiát használja majd, és lehetővé teszi a nagy sávszélességű memória (HBM) és más komponensek integrálását. A tervek szerint egy olyan nagy teljesítményű wafer-szintű rendszer jön létre, amelynek számítási teljesítménye egy teljes adatközpont szerverállványához hasonlítható.

A TSMC azt is elmondta, hogy a nagy sebességű összeköttetésekhez un. Compact Universal Photonic Engine (COUPE) technológiát fejleszt, és a mesterséges intelligenciát említette, mint olyan alkalmazást, amelynek erre szüksége lesz. A technológia a chipek egymásra helyezésével egy elektromos chipet egy fotonikai chip tetejére szerel fel. "A TSMC-nél a legátfogóbb technológiákat kínáljuk ügyfeleinknek az MI-vel kapcsolatos elképzeléseik megvalósításához, a világ legfejlettebb szilíciumától kezdve a fejlett tokozási és 3D-s IC-platformok legszélesebb portfólióján át a digitális világot a valós világgal integráló speciális technológiákig” - mondta C. C. Wei, a TSMC vezérigazgatója.

A TSMC a hónap elején a várakozásokat felülmúlva 2024 első negyedévéről éves összehasonlításban magasabb bevételről számolt be, és közölte, hogy arra számít, hogy az MI-képes PC-k és adatközpontok iránti kereslet a chipeladások növekedését okozza majd.

Az esemény főszereplője az A16 volt, mely a cég útitervének következő félvezető-feldolgozási technológiája. A betűszóban az A betű az angström rövidítése, egy nanométerben 10 angström van, így az A16 egy 1,6 nm-es eljárás - de a TSMC nem így hivatkozik rá. A TSMC ezt 2026-ban tervezi gyártásba venni, és az ebből készült szilícium 8-10 százalékos sebességnövekedést biztosít majd az N2P eljáráshoz képest, amely maga is a vállalat jövőre gyártásba kerülő 2 nm-es technológiájának továbbfejlesztett változata. A TSMC jelezte, hogy nincs szüksége az ASML legújabb High NA EUV fotolitográfiai gépeire az A16-os eljárásra való áttéréshez. Az iparágban egyesek azt sugallták, hogy az Intel le fogja előzni a TSMC-t, mert ők az első chipgyártó, amelyik ilyen géppel fog dolgozni.

A TSMC nyilvánosságra hozta, hogy az A16 a 2 nm-en bevezetésre kerülő tranzisztor dizájnt a Super Power Rail technológiával kombinálja majd. Ez utóbbi a vállalat "backside power" kialakítása, ahol a tranzisztorokhoz áramot szállító sávokat a szilícium hátoldalára helyezik át, hogy több jelsávnak adjanak helyet. Az Intel tavaly mutatta be az ilyen megoldását. Ez jobb logikai sűrűséget és teljesítményt kínál azáltal, hogy az elülső oldali útválasztást a jeleknek szenteli, így az A16 ideális az összetett jelútvonalakkal és sűrű tápellátó hálózatokkal rendelkező HPC-termékekhez - közölte a TSMC.

Az N2, azaz 2 nanométeres eljáráshoz a TSMC bejelentette a NanoFlexnek nevezett tervezési optimalizálási technikát. Ez rugalmasságot biztosít a chiptervezőknek a szabványos cellák építőblokkjaiban, lehetővé téve számukra, hogy a nagyobb energiahatékonyságot biztosító kisebb, és a maximális teljesítményt biztosító nagyobb cellák kombinációját úgy hangolják, hogy a legjobb teljesítmény- és területkompromisszumot érjék el az alkalmazásukhoz. A félvezetőóriás a 4 nm-es gyártástechnológiáját is frissítette, itt az újdonság neve N4C. Ez olyan területhatékony tervezési szabályokat tartalmaz, amelyek kompatibilisek a népszerű N4P eljárással, de a TSMC állítása szerint 8,5 százalékos gyártási költség-csökkenést eredményeznek. A sorozatgyártás beindítását 2025-re tervezik.

Csomagolástechnológia terén a TSMC bejelentette, hogy már gyártják az első System-on-Wafer (SoW) ajánlatukat, ami lehetővé teszi, hogy egy 300 mm-es ostyán nagyszámú lapka egyetlen rendszert alkosson. Ez növeli a számítási teljesítményt, miközben sokkal kevesebb helyet foglal. A vállalat közölte, hogy a tervek szerint 2027-re elkészül a Chip-on-Wafer változat, amely a Chip-on-Wafer-on-Substrate (CoWoS) technológiát használja majd, és lehetővé teszi a nagy sávszélességű memória (HBM) és más komponensek integrálását. A tervek szerint egy olyan nagy teljesítményű wafer-szintű rendszer jön létre, amelynek számítási teljesítménye egy teljes adatközpont szerverállványához hasonlítható.

A TSMC azt is elmondta, hogy a nagy sebességű összeköttetésekhez un. Compact Universal Photonic Engine (COUPE) technológiát fejleszt, és a mesterséges intelligenciát említette, mint olyan alkalmazást, amelynek erre szüksége lesz. A technológia a chipek egymásra helyezésével egy elektromos chipet egy fotonikai chip tetejére szerel fel. "A TSMC-nél a legátfogóbb technológiákat kínáljuk ügyfeleinknek az MI-vel kapcsolatos elképzeléseik megvalósításához, a világ legfejlettebb szilíciumától kezdve a fejlett tokozási és 3D-s IC-platformok legszélesebb portfólióján át a digitális világot a valós világgal integráló speciális technológiákig” - mondta C. C. Wei, a TSMC vezérigazgatója.

A TSMC a hónap elején a várakozásokat felülmúlva 2024 első negyedévéről éves összehasonlításban magasabb bevételről számolt be, és közölte, hogy arra számít, hogy az MI-képes PC-k és adatközpontok iránti kereslet a chipeladások növekedését okozza majd.